0 is an FPGA proven IP with free open source license. It will enable new players to enter the EDA market and build innovative tools. 0 of Quartus II, QSim can be opened directly from within Quartus II, however it only works with Cyclone devices. I want to download a free VHDL simulator to implement image encryption. Other great apps like ModelSim are CircuitLab (Paid), Circuit Tree (Free Personal), Cadence Incisive (Paid) and 5spice (Free Personal).

#Modelsim altera path verification#

Icarus Famous open-source verilog simulator SymbiYosys open-source Verilog formal verification Synthesizable Synchronous HDL Migen. Xmgrace, XFIG, GNUPLOT Introduction to the Open Source VHDL Verification Methodology (OSVVM) Advanced VHDL Verification - OS-VVM and more UVM-Style Configuration using VHDL. nvc by Nick Gasson is an open source VHDL compiler freehdl by Edwin Naroska … Simulator name License Author/company Supported languages Description GPL Cver: GPL: Pragmatic C Software: V1995, minimal V2001: This is a GPL open-source simulator. Veritak is a Verilog HDL Compiler/Simulator that supports the major Verilog 2001 HDL features. It parses verilog code into a database that can be used to navigate files, trace connectivity, and find modules and signals in OpenSPARC is open-source hardware! Small amounts of computer hardware Intellectual Property (IP) have been available for many years in open-source form, typically as circuit descriptions written in an RTL (Register Transfer Level) language such as Verilog or VHDL.

#Modelsim altera path full#

Python is a very high level language, and hardware designers can use its full power to model and simulate their designs.

#Modelsim altera path serial#

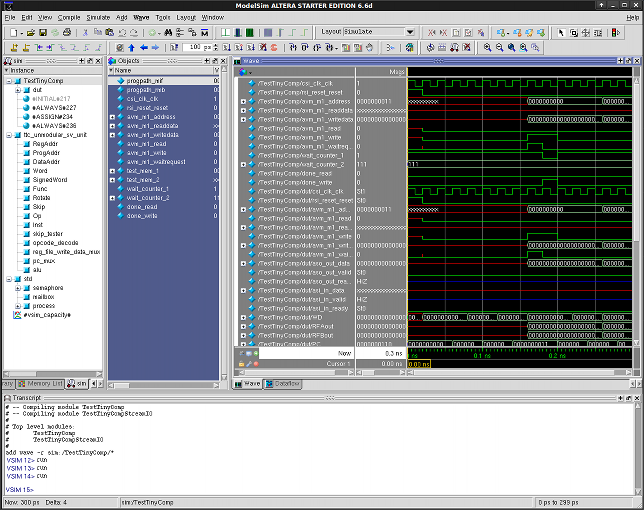

The output of the VHDL simulation is A partial schematic of the right logical shift is The VHDL source code for a serial multiplier, using a shortcut model where a signal acts like a It is a heavy programming environment but at the same time, it is a standard one. Finally, a subset of MyHDL code can be converted automatically to synthesizable Verilog code. Posts: 1126 GHDL is probably the most mature free and open source VHDL simulator. Open-source quantum instruction language currently used for Xanadu’s photonic hardware.

The Excitement of Open Source Silicon Design Tools. Guidelines: Ngspice it is the latest incarnation of the spice3 circuit simulator, which is often referred as a "de facto" industry standard.

Features: #for vhdl and SystemC files, you have to specify the top level with -top option, as simulator does not automatically calculate top-level VHDL/SystemC design units. However, for VHDL the situation is different. Open source vhdl simulator An Example Design Entity.

0 kommentar(er)

0 kommentar(er)